# AMC Data Processing and Telecommunication Module

**DAMC-TCK7**

#### **FEATURES**

#### **Advanced Mezzanine Card (AMC)**

Powerful Kintex-7 FPGA (XC7K355T or XC7K420T)

2 Gigabytes of DDR3 SDRAM

8x SFP+ on front panel (10 Gbps \*)

PCIe x4 gen. 3 (8 Gbps)

2 channels of Gigabit Ethernet (1 Gbps)

10 direct low latency connections to backplane (10Gbps\*)

4 low latency connections to RTM (10 Gbps \*)

LVDS parallel bus to RTM (28 lanes)

Partial reconfiguration and firmware upgrade support

Advanced diagnostic, monitoring and debugging

#### Options:

- XC7K355T-FGG901

- XC7K420T-FGG901

Board Support Package under <a href="https://github.com/MicroTCA-Tech-Lab/damc-tck7-fpga-bsp">https://github.com/MicroTCA-Tech-Lab/damc-tck7-fpga-bsp</a>

The AMC-based Controller (DAMC-TCK7) board is a general purpose high-performance low-latency data processing unit designed according to the PICMG MTCA.4 specifications. The module provides processing power, data memory, communication links and reference clock signals. The module was originally designed as a LLRF (Low Level Radio Frequency) cavity field stabilizing controller for standing-wave linear accelerators. However, the application of the board is much wider for systems requiring low latency and high speed digital signal processing.

The Xilinx FPGA (Field Programmable Gate Array) device available on the DAMC-TCK7 board delivers a computing power and memory for low-latency digital signal processing. The FPGA supports a number of Low Latency Links (LLLs) available on the front panel, at the backplane and a Rear Transition Module (RTM) Zone 3 connector, working with a few Gbps throughput.

DESY offers the DAMC-TCK7 for licensing to industry. DESY can modify this product to meet special customer requirements.

<sup>\*</sup> possible 12.5 Gbps with Kintex-7 speed grade -3

### AMC Data Processing and Telecommunication Module DAMC-TCK7

### TECHNICAL SPECIFICATIONS

|                       |                           |                                  | Double width, Mid-Size with Full-Size option            |

|-----------------------|---------------------------|----------------------------------|---------------------------------------------------------|

| Physical              |                           | Dimensions                       | Width: 5.486" (148.5 mm)                                |

|                       |                           |                                  | Depth: 7.110" (180.6 mm)                                |

| Standards             |                           | MTCA.4                           | Advanced Mezzanince Card IPMI Version 2.0               |

|                       |                           | Module management                |                                                         |

| Compatibility         |                           | Zone 3 classification            | Class D1.2                                              |

| HANNELS               |                           | Compatible RTM products          | DRTM-VM2, DRTM-AD84, DRTM-PZT4                          |

| MAININELS             |                           | Number of communication channels | 28                                                      |

| Туре                  | Data Processing<br>Module | Total throughput                 | 350 Gbps                                                |

|                       |                           | FPGA resources                   | Slices: 65, 150, DSP slices: 1,680                      |

| Electrical properties |                           | Power consumption                | <24 W                                                   |

|                       |                           | Typical latency                  | <2 us                                                   |

|                       | FPGA                      | Xilinx Kintex-7                  | XC7K355T or XC7K420T                                    |

| Components            | RAM                       | DDR3-1066 SDRAM                  | 256 M x 64 bit                                          |

|                       | PROM                      | QSPI FLASH                       | 2 x 256 Mbit                                            |

|                       | clock reference           | Oscillator                       | 50 MHz                                                  |

|                       |                           | PLL                              | 2x quad output PLL                                      |

|                       |                           | Frequency                        | 30 – 325 MHz                                            |

|                       |                           | Jitter                           | <134 dBc/Hz@1 MHz                                       |

|                       |                           | Configuration interface          | I <sup>2</sup> C                                        |

| ONNECTIVIT            | Υ                         | - U                              |                                                         |

|                       | Low latency connection    | Front panel                      | 8 channels                                              |

|                       |                           | connector type                   | SFP+ cage, optical fibre                                |

|                       |                           | Data throughput                  | 10 Gbps (12.5 Gbps)                                     |

|                       |                           | Bit error rate                   | <10 <sup>14</sup> bit <sup>-1</sup>                     |

|                       | Reference clock           | Front panel                      | 1 channel                                               |

| Front panel           |                           | Connector type                   | SMA, single-ended                                       |

|                       |                           | Impedance/coupling               | 50 Ω/AC                                                 |

|                       |                           | Maximum input power level        | 1 dBm                                                   |

|                       | Debug interface           | Front panel                      | 2 channel, FPGA and MMC                                 |

|                       |                           | Connector type                   | Micro USB                                               |

|                       |                           | Data throughput                  | 3 Mbps                                                  |

|                       | Low latency connection    | Backplane                        | 8 channels                                              |

|                       |                           | Interface type                   | Peer-to-peer, ports 8-15 according to AMC specification |

|                       |                           | Data throughput                  | 10 Gbps (12.5 Gbps)                                     |

|                       |                           | Bit error rate                   | <10 <sup>14</sup> bit <sup>-1</sup>                     |

|                       | Low latency connection    | Backplane                        | 2 channels                                              |

|                       |                           | Interface type                   | Peer-to-peer, ports 2-3 according to AMC specification  |

| a alvala a a          |                           | Data throughput                  | 10 Gbps                                                 |

| ackplane              |                           | Bit error rate                   | <10 <sup>14</sup> bit <sup>-1</sup>                     |

|                       | PCIe                      | Backplane                        | 4 lanes                                                 |

|                       |                           | Interface type                   | PCle gen. 3.0                                           |

|                       |                           | Data throughput                  | 8 Gbps x 4                                              |

|                       |                           | Bit error rate                   | <10 <sup>14</sup> bit <sup>-1</sup>                     |

|                       | Gigabit Ethernet          | Backplane                        | 2 channels                                              |

|                       |                           | Data throughput                  | 1 Gbps                                                  |

## AMC Data Processing and Telecommunication Module DAMC-TCK7

### TECHNICAL SPECIFICATIONS

|                  | Low latency connection | RTM                         | 8 channels                                               |

|------------------|------------------------|-----------------------------|----------------------------------------------------------|

|                  |                        | Connector type              | Peer-to-peer, ports 8-15 according to D1.2 digital class |

|                  |                        | Data throughput             | 10 Gbps (12.5 Gbps)                                      |

|                  |                        | Bit error rate              | <10 <sup>14</sup> bit <sup>-1</sup>                      |

|                  | Parallel bus           | RTM                         | 38 differential pairs                                    |

|                  |                        | Connector type              | LVDS                                                     |

|                  |                        | Data throughput             | 38 Gbps                                                  |

| no 2             |                        | Bit error rate              | <10 <sup>14</sup> bit <sup>-1</sup>                      |

| ne 3             | AMC clock              | Clock output                | 2 reference clock signals                                |

|                  |                        | Connector type              | LVDS                                                     |

|                  |                        | Clock frequency             | 50 325 MHz / TCLKA                                       |

|                  | RTM clock              | Clock input                 | 2 reference clock inputs                                 |

|                  |                        | Clock type                  | FPGA global clock, GTX reference clock, PLL              |

|                  | Others                 | MTCA.4 signals              | IPMI bus - I <sup>2</sup> C, presence, power supply      |

|                  |                        | Interlocks                  | dedicated output signals                                 |

|                  |                        | JTAG                        | JTAG chain, +3V3                                         |

| IER FEATUR       | RES                    |                             |                                                          |

|                  |                        | Power supply management     | Via PMBUS                                                |

|                  |                        | RTM management              | With power supply and curent monitoring                  |

|                  |                        | Firmware upgrade            | Yes, via IPMI and PCIe interface                         |

| n board          |                        | Voltage and current monitor | Yes, readout via IPMI                                    |

|                  |                        | Clock monitoring            | Yes, readout via IPMI                                    |

|                  |                        | LEDs                        | IPMI management control                                  |

|                  |                        | Mechanical                  | Hot swap ejector handle                                  |

|                  |                        | Operating temperature       | 0 50 °C                                                  |

| nvironmental     |                        | Storage temperature         | -40 +90 °C                                               |

| iiviioiiiieiitai |                        | Relative humidity           | 5 90 %, non-condensing                                   |

|                  |                        | Weight                      | 0.7 kg                                                   |

| IER              |                        |                             |                                                          |

| ompliance        | RoHS                   |                             |                                                          |

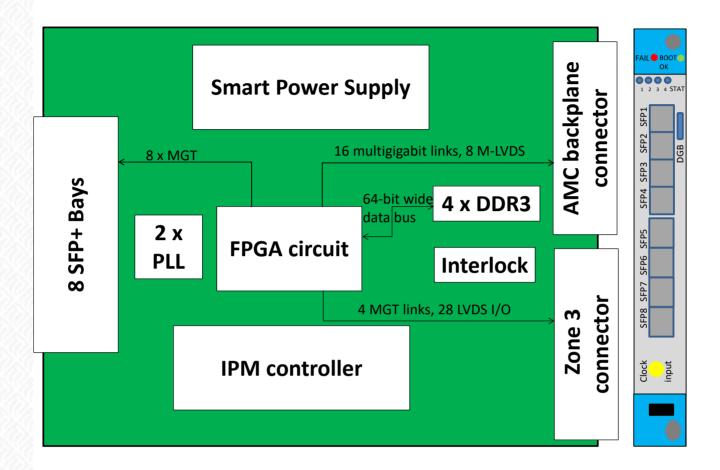

### AMC Data Processing and Telecommunication Module DAMC-TCK7

### FUNCTIONAL BLOCK DIAGRAM AND FRONT PANEL

### **OPTIONS**

| FPGA type      | FPGA speed grade   |

|----------------|--------------------|

| 355 = XC7K355T | 1 = speed grade -1 |

| 420 = XC7K420T | 2 = speed grade -2 |

|                | 3 = speed grade -3 |