# **DMMC-STAMP**

**User Manual**

Version 3.8

# **Table of Contents**

| Rev               | vision History                                   | 6  |

|-------------------|--------------------------------------------------|----|

| 1.                | Introduction                                     | 7  |

| 1.1               | Block Diagram                                    | 7  |

| 1.2               | Module Features                                  | 8  |

| 1.3               | Operating Conditions                             | 9  |

| 2.                | Management in MicroTCA®                          | 10 |

| 3.                | Module Component Description                     | 11 |

| 3.1               | Microcontroller                                  | 11 |

| 3.2               | CPLD                                             | 11 |

| 3.3               | USB-to-UART Bridge                               | 12 |

| 3.4               | RTM Hot-Plug Controller                          | 12 |

| 3.5               | Power System                                     | 12 |

| 3.6               | Debug Access Port                                | 14 |

| 3.7               | On-Board LEDs                                    | 15 |

| 4.                | LGA Footprint                                    | 16 |

| 4.1               | Layout Information                               | 18 |

| 4.2               | Stencil information                              | 19 |

| <b>5</b> .        | Module Interface Description                     | 20 |

| 5.1               | MicroTCA® and AMC Pins                           | 20 |

| 5.2               | Power Pins                                       | 22 |

| 5.2.              | 1 Global Power and Ground Routing Considerations | 24 |

| 5.3               | Target AMC Power Management Pins                 | 25 |

| 5.4               | FPGA/SoC Pins                                    | 27 |

| 5.4.              | '                                                |    |

| 5.4.2             |                                                  |    |

| 5.5               | RTM Pins                                         |    |

| 5.5. <sup>2</sup> | • •                                              |    |

| 5.5. <sub>2</sub> | FMC Pins                                         |    |

| 5.7               | Debug Pins                                       |    |

| 5.8               | Interlock forwarding to RTM                      |    |

| 5.8. <sup>2</sup> | -                                                |    |

| 5.8.2             | ·                                                |    |

| 5.8.3          | 3 Interlock Forwarding Configuration inside DMMC-STAMP | 44 |

|----------------|--------------------------------------------------------|----|

| 5.9            | Pre-Installed Firmware                                 | 45 |

| 5.10           | Full IPMI Stack                                        | 45 |

| 5.10           | 0.1 Sensor Data Records (SDR)                          | 45 |

|                | 0.2 System Event Generator                             |    |

| 5.11           | Command Line Interface                                 | 47 |

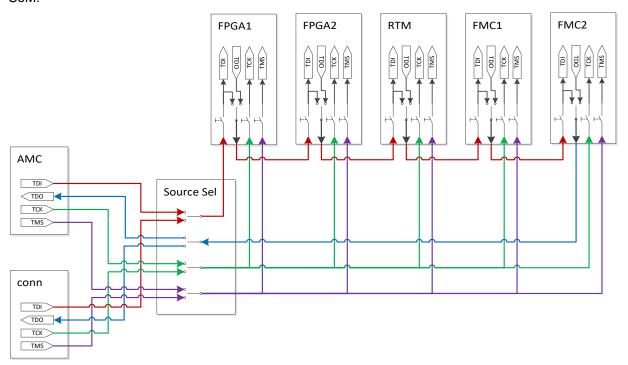

| 5.12           | Reconfigurable JTAG Chain                              | 48 |

| 5.13           | Out-of-Crate Mode                                      | 49 |

| 6.             | Development Tools                                      | 50 |

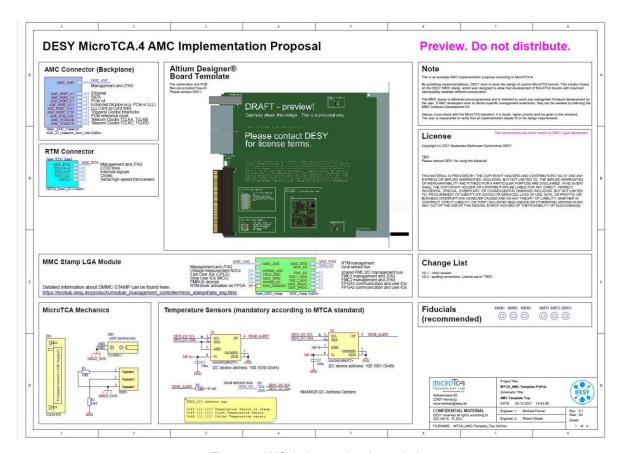

| 6.1            | Hardware Design Templates                              | 50 |

| 6.1.1<br>6.1.2 | 3 1 1                                                  |    |

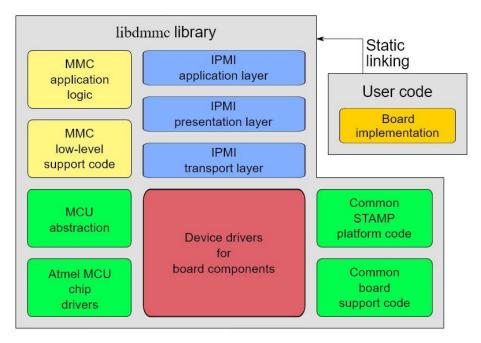

| 6.2            | DMMC-SDK (Software Development Kit)                    | 51 |

| 6.3            | DMMC-STAMP Breakout Board                              | 54 |

| 6.4            | MMC Terminal (mmcterm)                                 | 55 |

| 6.5            | FRU Generator YAML (frugy)                             | 56 |

| 6.6            | HPM File Generator (bin2hpm)                           | 57 |

| 6.7            | LGA Pinout                                             | 59 |

| 6.8            | Abbreviated Schematics                                 | 61 |

| <b>7</b> .     | References                                             | 63 |

| lmp            | orint                                                  | 64 |

# **Figures**

| Figure 1: DMMC-STAMP System on a Module (SoM)                         | 7  |

|-----------------------------------------------------------------------|----|

| Figure 2: DMMC-STAMP Block Diagram                                    | 7  |

| Figure 3: DMMC-STAMP (Revision A) components                          | 8  |

| Figure 4: AMC module management hardware components                   | 10 |

| Figure 5: DMMC-STAMP power tree                                       | 13 |

| Figure 6: MCU Debug (Tag-Connect pads)                                |    |

| Figure 7: DMMC-STAMP On-Board LEDs                                    |    |

| Figure 8: DMMC-STAMP Pad Naming                                       | 16 |

| Figure 9: DMMC-STAMP Dimensions                                       |    |

| Figure 10: DMMC-STAMP Pad Geometry (except pad A1)                    | 18 |

| Figure 11: DMMC-STAMP Pad A1 Geometry                                 | 18 |

| Figure 12: AMC connector pins                                         | 20 |

| Figure 13: MicroTCA® mandatory components                             | 20 |

| Figure 14: DMMC-STAMP SoM power input/output pins                     |    |

| Figure 15: DMMC-STAMP Power and Ground connection using Type VII vias |    |

| Figure 16: DMMC-STAMP Power and Ground connection using standard vias | 24 |

| Figure 17:DMMC-STAMP power management pins                            |    |

| Figure 18: DMMC-STAMP FPGA/SoC interface pins                         | 29 |

| Figure 19: SPI Flash configuration memory connection scheme           |    |

| Figure 20: SPI Flash multiplexer implementation                       |    |

| Figure 21: SPI Flash implementation                                   | 32 |

| Figure 22: RTM interface pins                                         | 33 |

| Figure 23: RTM power routing example using Type VII vias              | 35 |

| Figure 24: RTM power routing example using standard vias              | 36 |

| Figure 25: FMC interface pins                                         | 37 |

| Figure 26: DMMC-STAMP debug interfaces                                |    |

| Figure 27: DMMC-STAMP debug interfaces                                | 39 |

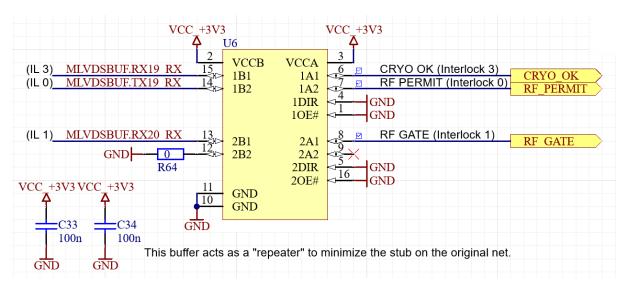

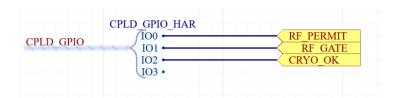

| Figure 28: Typical M-LVDS Implementation                              | 41 |

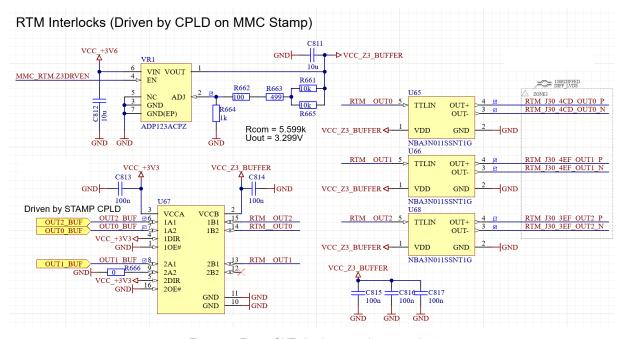

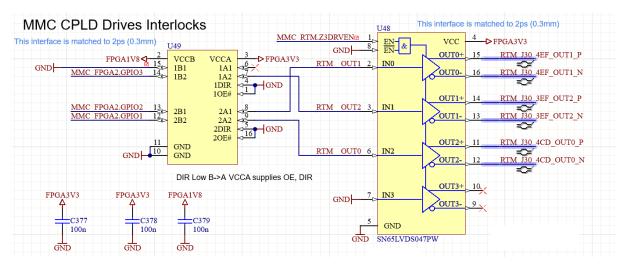

| Figure 29: Typical "M-LVDS-copy-to-RTM" implementation                | 42 |

| Figure 30: Outputs of M-LVDS receivers connection to DMMC-STAMP       |    |

| Figure 31: Zone3 OUTx Implemenatation example 1                       | 43 |

| Figure 32: Zone3 OUTx Implemenatation example 2                       | 44 |

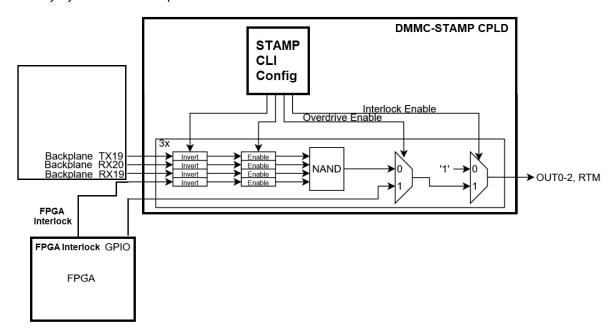

| Figure 33: Interlock Logic on DMMC-STAMP                              | 44 |

| Figure 34: Reconfigurable JTAG chain (Source Sel = DMMC-STMAP SoM)    | 48 |

| Figure 35: Bring-up mechanics and bring-up adapter (backplane dummy)  | 49 |

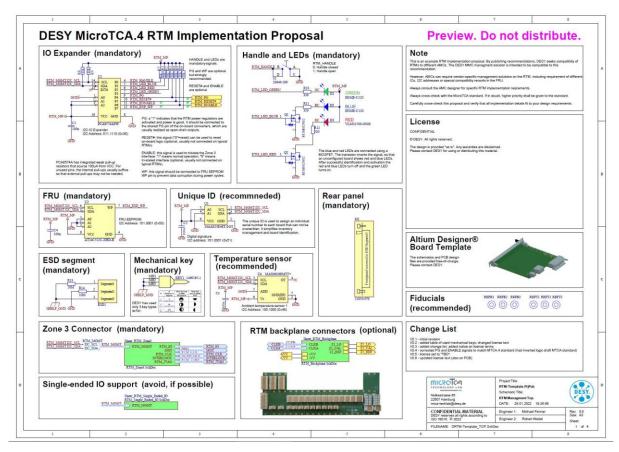

| Figure 36: AMC design template (exception)                            | 50 |

| Figure 37: RTM design template (exception)                            | 51 |

| Figure 38: DMMC-SDK code structure (simplified)                       | 53 |

| Figure 39 : DMMC-STAMP-Breakout-Board Rev. C                          |    |

| Figure 40: DAMC-FMC2ZUP YAML configuration file (abbreviated)         | 57 |

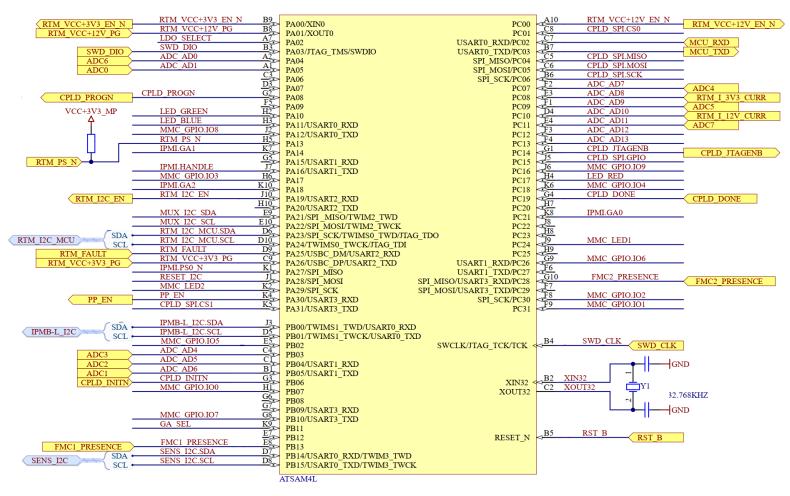

| Figure 41: MCU pin-out                                                | 61 |

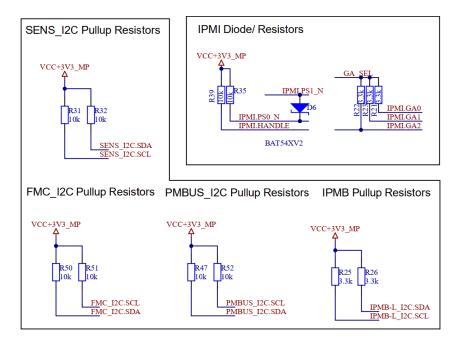

| Figure 42: DMMC-STAMP pull-ups                                        | 61 |

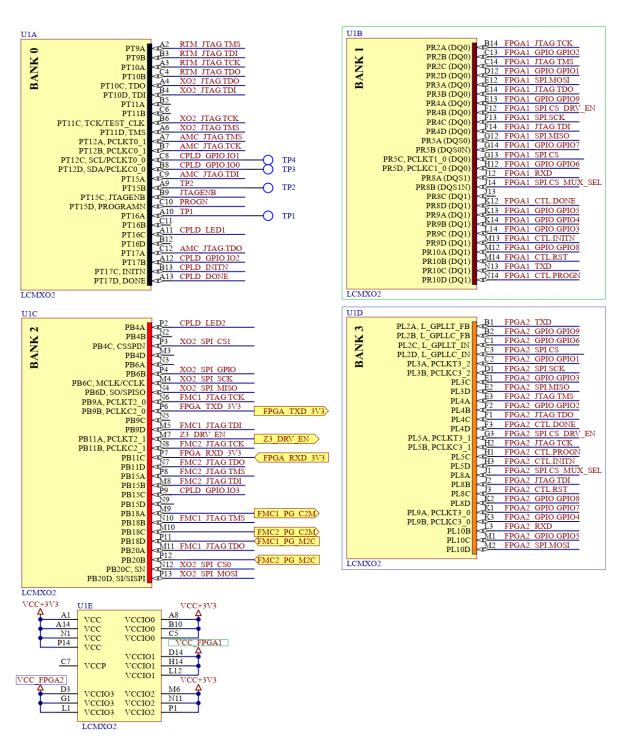

| Figure 43: CPLD pin-out                                               | 62 |

### **Tables**

| Table 1: DMMC-STAMP operating conditions                                 | 9  |

|--------------------------------------------------------------------------|----|

| Table 2: MCH/Backplane interface pin description                         | 21 |

| Table 3: Handle and LED pin description                                  | 21 |

| Table 4: Sensor interface pin description                                | 22 |

| Table 5: AMC JTAG pin description (CPLD pins indicated in green)         | 22 |

| Table 6: Power Pin Description                                           | 23 |

| Table 7: Target AMC PMBUS™ Pin Description                               | 26 |

| Table 8: ADC pin description for target AMC power monitoring             | 26 |

| Table 9: Low-speed MCU GPIO pin description                              | 26 |

| Table 10: High-speed CPLD GPIO pin description                           | 27 |

| Table 11: FPGA/SoC UART pin description                                  | 29 |

| Table 12: FPGA/SoC JTAG pin description                                  | 29 |

| Table 13: FPGA/SoC Control pin description                               | 30 |

| Table 14: FPGA/SoC GPIO pin description                                  | 30 |

| Table 15: FPGA/SoC SPI Flash control pin description                     | 31 |

| Table 16: RTM power pin description                                      | 33 |

| Table 17: RTM management signal pin description                          | 33 |

| Table 18: FPGA/SoC tri-state control pin description                     | 34 |

| Table 19: RTM JTAG pin description                                       | 34 |

| Table 20: FMC management pin description                                 | 37 |

| Table 21: FMC JTAG pin description                                       | 38 |

| Table 22: Central JTAG connector pin description                         | 39 |

| Table 23: USB connector pin description                                  | 39 |

| Table 24: SWD pin description                                            | 40 |

| Table 25: DESY-Specific M-LVDS assignment                                | 41 |

| Table 26: FRU date structure                                             | 46 |

| Table 27: Differences DMMC-STAMP SoM pre-installed firmware and DMMC-SDK | 52 |

# **Revision History**

| Revision | Date       | Description of Change                                                                                                                                                                           |  |  |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0      | 09/09/2019 | Initial Release                                                                                                                                                                                 |  |  |

| 1.1      | 14/11/2019 | Add block diagrams, pin descriptions and clarifications                                                                                                                                         |  |  |

| 2.0      | 18/05/2021 | Various improvements                                                                                                                                                                            |  |  |

| 2.1      | 26/06/2021 | Minor corrections based on review                                                                                                                                                               |  |  |

| 2.2      | 19/10/2021 | Add footprint, SDK and design template information                                                                                                                                              |  |  |

| 2.3      | 03/08/2022 | Correct SDK information table, update dimension drawing                                                                                                                                         |  |  |

| 3.0      | 28.09.2022 | Refurbish the manual, add standard firmware information                                                                                                                                         |  |  |

| 3.1      | 14.04.2023 | Add SWD pin numbers; improvements of pin-out table (B3, I3, C3, N2, N3, N4, D3); Add compact pinout table                                                                                       |  |  |

| 3.1.1    | 23.12.2023 | Modify imprint, add copyright, switch to "Only Office".                                                                                                                                         |  |  |

| 3.2      | 17.09.2024 | Add information about I2C busses and update block diagram.                                                                                                                                      |  |  |

| 3.2.1    | 16.01.2025 | Minor fonts touch-up                                                                                                                                                                            |  |  |

| 3.3      | 22.04.2025 | Correct CPLD_IOx table, add stencil information, minor corrections                                                                                                                              |  |  |

| 3.4      | 22.09.2025 | Add info anbout outlet temp sensor and its I2C address. Remove one stencil recommendation (manufacturer feedback). Add Information on DMMC- STAMP Mailbox. Update imprint about AI tools usage. |  |  |

| 3.5      | 22.09.2025 | Add information about integrated pull-up and pull-down resistors. Add "References" chapter.                                                                                                     |  |  |

| 3.6      | 5.10.2025  | Add information about Interlock implementation; update DMMC-BoB image and text                                                                                                                  |  |  |

| 3.7      | 10.11.2025 | Document Out-of-Crate Mode, add SDK-related note on FMC pins , document CPLD pins and add abbreviated schematifcs                                                                               |  |  |

| 3.7.1    | 27.11.2025 | Minor touch-up of graphics and images without information update.                                                                                                                               |  |  |

| 3.8      | 11.12.2025 | Minor text touch-up, add power routing information (general and RTM), add mailbox address, and power supply details (general and RTM).                                                          |  |  |

### 1. Introduction

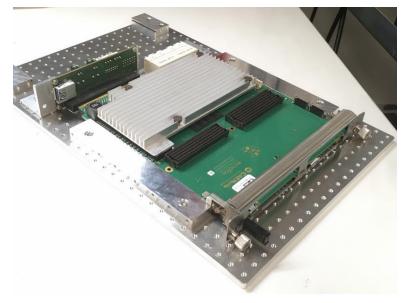

The DESY Module Management Controller System on Module (DMMC-STAMP SoM) provides a full management solution for operating the targeted Advanced Mezzanine Card (AMC) in a MicroTCA-based ecosystem. The module itself is a small, stamp-sized ( $25.5 \times 29.5 \times 2.3$  mm) component that can be mounted on the top or bottom side of any AMC PCB. In addition to the management features required by the MicroTCA specification, the DMMC-STAMP can operate the AMC power system, manage up to two FPGAs/SoCs, and host up to two slots for FPGA Mezzanine Cards (FMCs) and one Rear Transition Module (RTM).

Figure 1: DMMC-STAMP System on a Module (SoM)

### 1.1 Block Diagram

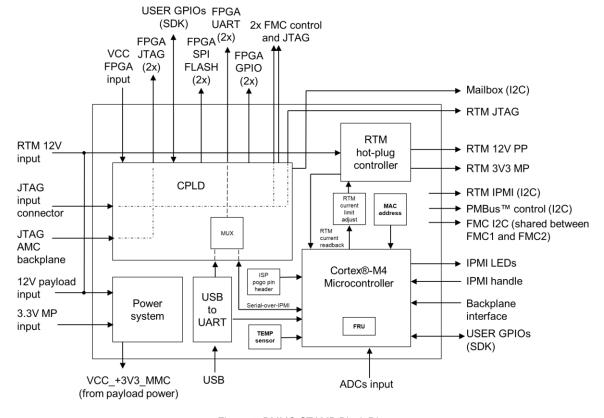

The DMMC-STAMP System on a Module (SoM) block diagram is shown in Figure 2.

Figure 2: DMMC-STAMP Block Diagram

### 1.2 Module Features

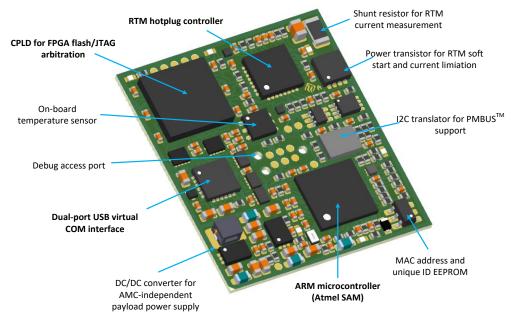

The DMMC-STAMP SoM features are listed here:

- Full IPMI handling (MCH communication, LEDs, AMC/RTM power, FRU read/write)

- On-board 12-bit temperature sensor

- On-board 1kBit EEPROM (memory for non-volatile settings)

- Hard-coded 48-bit unique ID that can be used as MAC Address by FPGA (SDK required)

- 8 analog inputs (0-1V) for voltage measurement; management power (3.3V MP) and payload power (12V PP) are measured on the DMMC-STAMP by using additional ADC channels

- Board failure handling (over-current and over-temperature detection)

- Support of up to two FPGA/SoC interfaces (custom interface voltage: 1.2V 3.3V), including IPMI firmware update of associated SPI FLASH memories and 8 GPIO pins per interface

- Control of up to two FMC modules (optional)

- · Re-configurable JTAG chain management

- RTM management including hot-swap controller with adjustable payload current limit

- 2-channel USB virtual COM port for MMC and FPGAs/SoCs and remote serial-over-IPMI mirroring

- Includes pre-programmed default MMC firmware that allows the user design to run inside MicroTCA

- A Software Development Kit (SDK) is optionally available to further customize DMMC-STAMP behavior, for example to support custom sensors or enable advanced interaction between the payload electronics (e.g., SoC) and MicroTCA management.

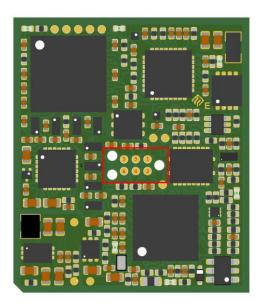

Figure 3: DMMC-STAMP (Revision A) components

# 1.3 Operating Conditions

The DMMC-STAMP SoM operating conditions are listed here:

### **Environmental**

| Operating Temperature                                     | 0 - 80°C                     |  |

|-----------------------------------------------------------|------------------------------|--|

| Minimum Airflow                                           | None                         |  |

| Electrical                                                |                              |  |

| Input Power (Payload)                                     | 12V nominal, 10V - 14V range |  |

| Input Power (Management)                                  | 3.3V +/- 10%                 |  |

| Output Voltage (VCC_+3V3_MMC)                             | 3.3V +/- 10%                 |  |

| Maximum Output Current (VCC_+3V3_MMC)                     | 250mA                        |  |

| Maximum voltage on all Digital input Pins                 | VCC +0.3V                    |  |

| Maximum voltage on FPGA supply pins                       | 3.3V                         |  |

| Maximum voltage on all analog input pins                  | 1.0V                         |  |

| Maximum sink/source current on all MCU Pins               | 3.2 mA                       |  |

| Maximum sink/source current on red/green/blue LED         | 24mA                         |  |

| Maximum output current on all CPLD Pins                   | 8 mA                         |  |

| RTM output current limit VCC_RTM+3V3_MP                   | 65mA (nominal)               |  |

| RTM output current limit range VCC_RTM+12V (user setting) | 1.62A (19.4W) - 4.60A (55W)  |  |

Table 1: DMMC-STAMP operating conditions

### 2. Management in MicroTCA®

MicroTCA® is a modular and open specification for electronics that provides advanced management features and modern communication interfaces. A characteristic feature of MicroTCA® is the out-of-band management, which significantly simplifies the maintenance and the collection of status information in large installations.

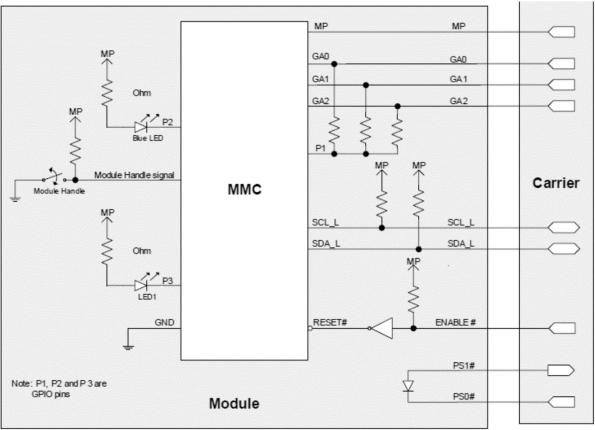

Important building blocks in a MicroTCA® based environment are the Advanced Mezzanine Cards® (AMC), as defined in the PICMG AMC.0 specification. AMCs usually contain FPGAs, SoCs, DSPs or other processing components to perform a desired functionality. Apart from this main "payload" and according to the specifications, a Module Management Controller (MMC) is required, to provide the AMC board management capabilities. Shown in Figure 4 (from PICMG AMC.0, copyright PICMG, used with permission) are the mandatory management components that have to be present on every AMC module.

Figure 4: AMC module management hardware components

All hardware components shown above (except of the LEDs and Module Handle) are integrated on the DMMC-STAMP SoM. As a reference for a custom AMC hardware development based on the DMMC-STAMP SoM the DESY MicroTCA Technology Lab provides an AMC design template for the Altium Designer® software. For more details see 6.1.

### 3. Module Component Description

This chapter provides a detailed functional description of the DMMC-STAMP SoM components and features. All components described here are already shown in Figure 2 and Figure 3.

### 3.1 Microcontroller

The DMMC-STAMP SoM is populated with an ATSAM4LS8C Cortex-M4 microcontroller. Configured with the pre-programmed DMMC-STAMP firmware it provides the following features:

- Low-power system, running at 36 MHz and 3.3V management power

- Full IPMI handling

- · Fail-safe in-system update mechanism

The integrated bootloader allows in-system firmware update (HPM) initiated by the user. The bootloader will take over all IPMI communication until a valid application has been programmed and loaded.

- Embedded FRU storage in internal FLASH memory

- 8 ADC channels with 12 bits resolution (0 1V input range) used for carrier power management

#### 3.2 **CPLD**

The DMMC-STAMP SoM is populated with a Lattice MachXO2 CPLD that handles the payload FPGA related functionality. Configured with the pre-programmed DMMC-STAMP firmware it provides the following features:

- Full isolation between management and payload power domains

- Complete FPGA/SoC handling (PROGRAM, INIT, DONE, ...)

- Two FPGA/SoC power domains with two user-defined voltage levels (i.e. fully independent power rails for the two FPGA/SoC interfaces)

- All pins of the FPGAs/SoCs can run at an arbitrary voltage (e.g. 1,2V, 1.8V, 3.3V), which is injected from the outside (CPLD bank voltage)

- UART interface to the user FPGAs/SoCs

- Control of the FPGA/SoC SPI FLASH memories (including HPM update)

- Control of the JTAG chain (including JTAG arbitration)

During the SoM power-up sequence the CPLD gets in-system programmed by the pre-programmed DMMC-STAMP firmware. The CPLD configuration file is part of every MMC firmware update file and the CPLD update itself is fully transparent to the user. The DMMC-STAMP firmware automatically ensures that the CPLD configuration matches the firmware version and re-programs it, if necessary.

### 3.3 USB-to-UART Bridge

The DMMC-STAMP SoM is populated with a Silicon Labs CP2105 dual channel USB-to-UART bridge. This interface has following properties:

- Channel 1: Command Line Interface (CLI) debug access to the Cortex-M4 microcontroller

- Channel 2: Command Line Interface (CLI) debug access to the USER FPGAs/SoCs

For managing up to two FPGAs/SoCs at USB-to-UART channel 2 the interfaces get multiplexed inside the DMMC-STAMP CPLD. In the pre-programmed DMMC-STAMP firmware the FPGA/SoC selection can be changed by using the USB CLI interface to the microcontroller (channel 1).

### 3.4 RTM Hot-Plug Controller

The RTM power is handled by a dedicated controller on the DMMC-STAMP. The features of this chip are listed here:

- RTM power handling (12V power is activated in M4 state)

- · RTM inrush current limiting

- Customizable maximum power limit (MCU-controlled I2C potentiometer)

- RTM over-current protection

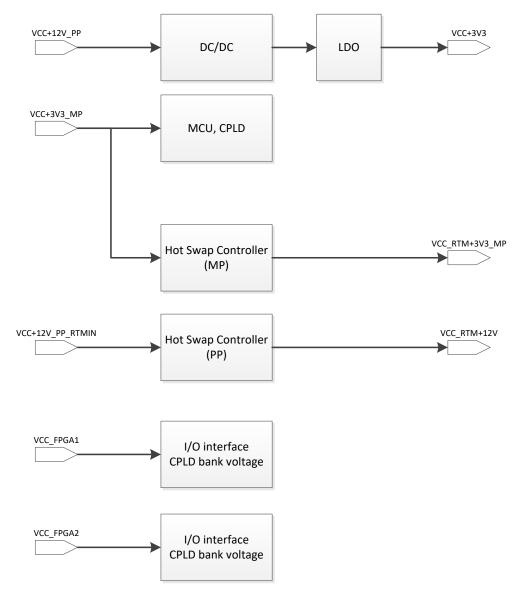

### 3.5 Power System

The Power System section deploys all required voltages to the DMMC-STAMP components. Furthermore, there is a 3.3V power output to the target AMC which gets available as soon as the payload power on the DMMC-STAMP is activated. Usually this 3.3V rail will be the first power domain (derived from payload power) that gets available on the target AMC. The 3.3V power domain can be used to run user-defined management electronics (e.g. LDO bias voltage or PMBUS controller power).

Additional information:

- The DMMC-STAMP MCU runs on the 3.3V management power (no other voltages needed).

- The DMMC-STAMP pre-programmed firmware will initiate all steps to the activate the 12V payload power.

- All additional voltages (derived from payload power) which are needed for operating the DMMC-STAMP are generated on-board (e.g. the CPLD core voltage is generated on-board).

- The DMMC-STAMP CPLD runs in the payload power domain.

- Voltages needed for operating FPGAs/SoCs on the target AMC are provided from external power input pins.

- VCC+3V3: 3.3V is generated from payload power by a dedicated DC/DC converter followed by an LDO stage. The user can draw up to 250mA current from this rail.

Figure 5: DMMC-STAMP power tree

If AMC boards are to be equipped with a DMMC-STAMP whose firmware is intended to be modified using the SDK, the custom DMMC-STAMP firmware is typically designed to manage the entire power tree. This can be implemented in a simple setup using an MCU GPIO pin as a global power enable/disable to initiate the power-on/ power-off sequence, or in a more advanced configuration using a PMBus™-controlled power tree. In all cases, both power activation and deactivation should be controlled through the DMMC-STAMP to ensure a coordinated and controlled shutdown while the board is still powered. If the power system is not managed by the DMMC-STAMP, power-down will usually occur abruptly, and there may not be enough time to safely shut down all power rails, potentially violating the sequencing requirements of the user's payload components.

### 3.6 Debug Access Port

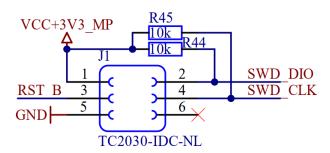

Integrated into the target AMC and during operation, the DMMC-STAMP gets programmed and updated by using the Intelligent Platform Management Interface (IPMI) provided by the MicroTCA® infrastructure. For debug and development purposes, the DMMC-STAMP PCB is equipped with landing pads for a Tag-Connect™ cable which provide access to the Serial Wire Debug (SWD) interface of the Microcontroller Unit (MCU).

#### Debug connector Pinout:

| 5: GND  | 3: RST_B   | 1: VCC+3V3_MP |  |  |

|---------|------------|---------------|--|--|

| 6: N.C. | 4: SWD CLK | 2: SWD DIO    |  |  |

The picture shows the TC2030 with "legs". They need to be removed to mate to the DMMC-STAMP

Figure 6: MCU Debug (Tag-Connect pads)

#### Additional information:

- The DMMC-STAMP SoM is designed to match with the TC2030-CTX-NL connector given here: https://www.tag-connect.com/product/tc2030-ctx-nl-6-pin-no-legs-cable-with-10-pin-micro-connector-for-cortex-processors

- The connector needs retainer clips:

https://www.tag-connect.com/product/tc2030-retaining-clip-board-3-pack

Alternative source from Digi-Key:

$https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CTX/TC2030-CTX-ND/5023324\\ https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CLIP/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CLIP/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CLIP/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CLIP/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CLIP/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/product-detail/de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/product-de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-llc/TC2030-CLIP-ND/2605371\\ https://www.digikey.de/tag-connect-ll$

These links point to the "legged" version of the cable. The legs can be simply removed to manually create no-legged version of the cable.

The one end of the cable needs to be plugged into the ATMEL-ICE ARM programmer. The

other end of the cable needs to connect to the SWD pads of the DMMC-STAMP.

### 3.7 On-Board LEDs

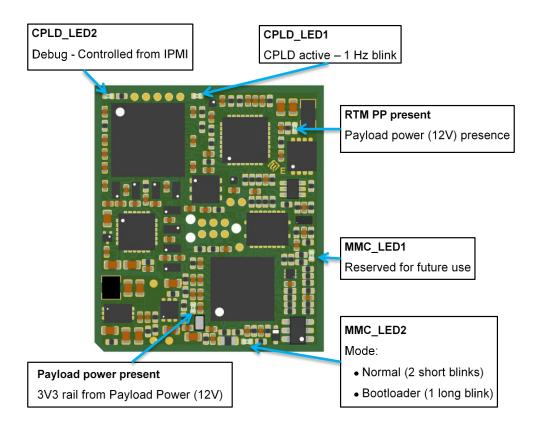

Described in Figure 7 are the DMMC-STAMP on-board LEDs:

Figure 7: DMMC-STAMP On-Board LEDs

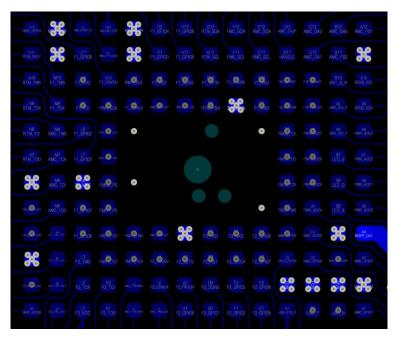

# 4. LGA Footprint

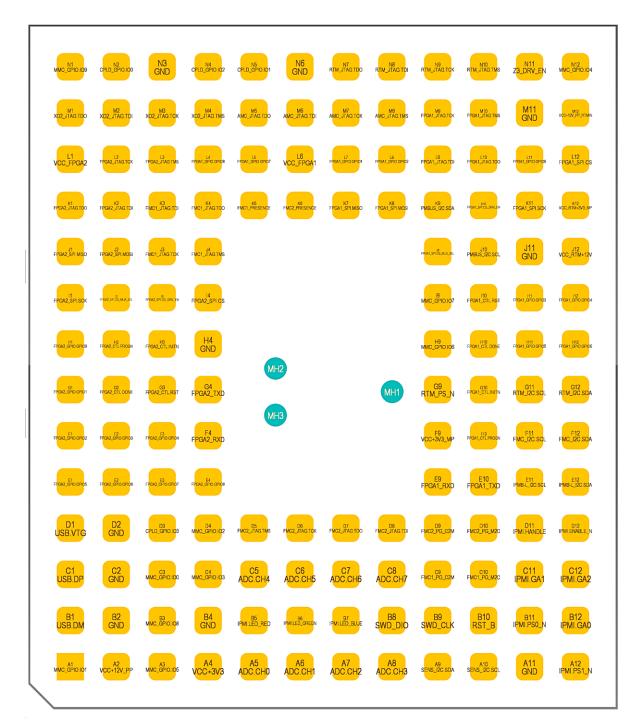

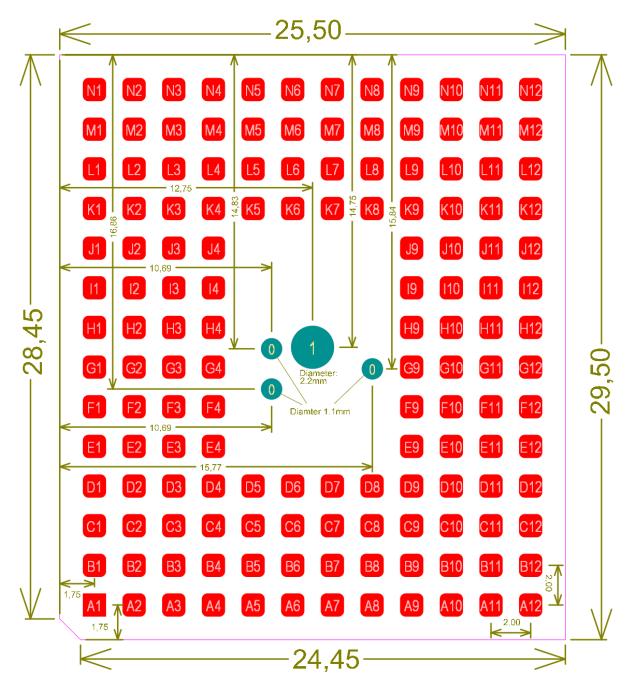

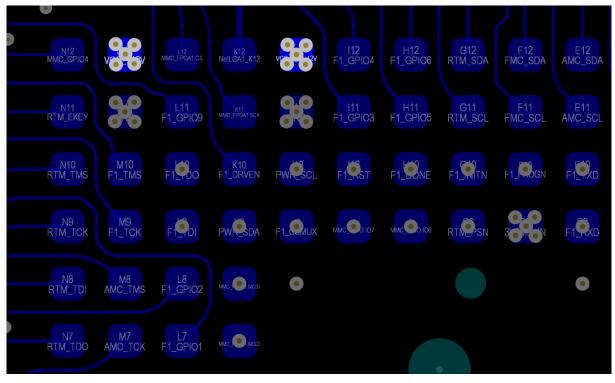

This chapter describes the Land Grid Array (LGA) footprint of the DMMC-STAMP. All drawings below show the pin assignment as seen from the top side of the module (view through the PCB).

Figure 8: DMMC-STAMP Pad Naming

Figure 9: DMMC-STAMP Dimensions

The hole marked with "1" is used for checking the alignment of the DMMC-STAMP SoM. The LGA contains a cross in the center, which shall be located in the middle of the hole within a correct assembly. Holes marked with "0" are the guide holes used by the Tag-Connect<sup>TM</sup> connector which can be plugged to the DMMC-STAMP SoM for debugging and development purposes. If used, the alignment pins will protrude the board and the retaining clip can be mounted below the user board.

The outer dimensions of the DMMC-STAMP SoM are given with a tolerance of +/- 0,5 mm.

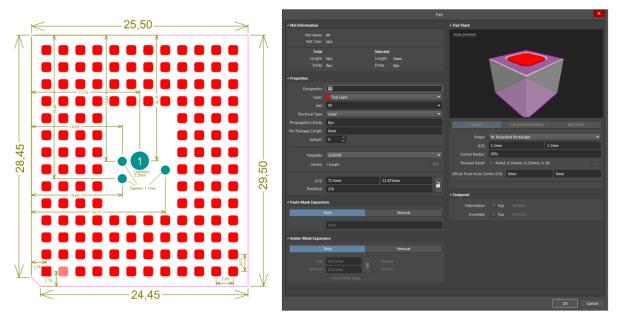

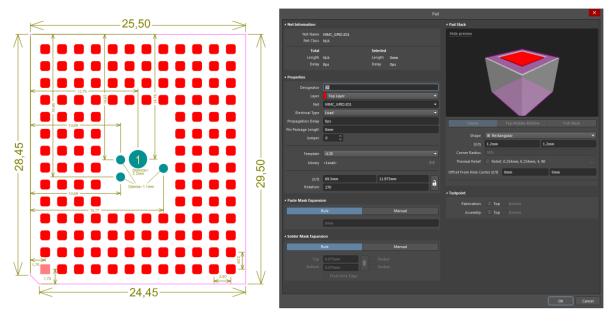

### 4.1 Layout Information

- A component clearance of 2 mm around the DMMC-STAMP SoM is recommended.

- It is strongly recommended to add the Tag-Connect™ alignment holes.

- Adding the center hole for checking the alignment is optional.

- All pads shall have a 2 mm pitch.

- The pad geometry (except pad A1) shall be 1.2 mm x 1.2 mm with rounded corners.

- The pad A1 geometry shall be 1.2 mm x 1.2 mm with a rectangular shape.

- Solder paste coverage of the complete pad is recommended.

- Non-solder mask defined pads with 0.075 mm mask expansion is recommended.

Figure 10: DMMC-STAMP Pad Geometry (except pad A1)

Figure 11: DMMC-STAMP Pad A1 Geometry

### 4.2 Stencil information

On AMC boards, the MMC stamp is one of the less critical parts in terms of stencil requirements. Usually, other parts define the stencil thickness and the stamp is used with the same stencil thickness.

DESY is aware of two different stencil designs used by its manufacturers and partners:

- 1. Standard 100µm stencil: A 100µm thick stencil with reduced solder mask opening is used solder mask opening is reduced to 90% to have an effective opening of 1.08x1.08mm with a radius of 270µm.

- 200um/100um step stencil: A milled paste stencil at 0.200μm thickness is used. The LGA stamp module is soldered at full 200μm thickness and the rest of the stencil is milled down to 100μm thickness.

These are two three examples that have been used successfully. Other stencil types and thicknesses may also give good results.

### 5. Module Interface Description

This chapter provides a detailed description of the DMMC-STAMP SoM interfaces. CPLD pins (customizable via DMMC-STAMP SDK) have green background.

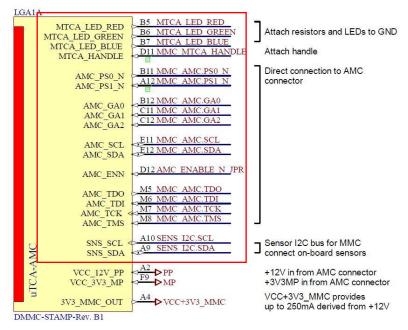

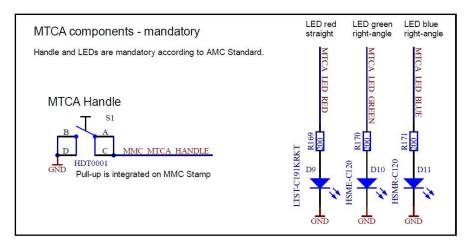

### 5.1 MicroTCA® and AMC Pins

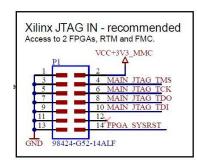

The MTCA and the AMC interfaces provide all signals that are to be connected to the backplane and to the IPMI-related user interface (LEDs, handle). All items listed below are mandatory (except of the JTAG signals). The JTAG interface provides access to the DMMC-STAMP SoM CPLD. Equipped with the appropriate configuration logic the CPLD provides access to the complete user JTAG chain of the target AMC which can include FPGAs/SoCs or devices on the RTM and FMC modules.

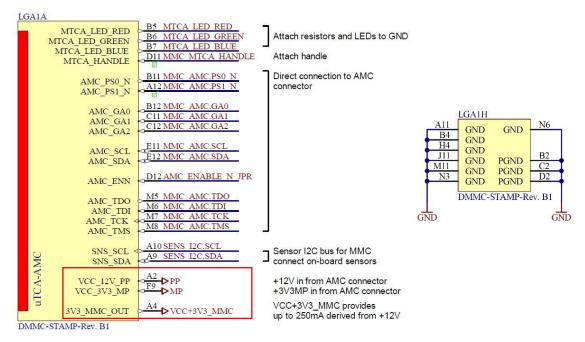

Shown in Figure 12 and Figure 13 are exceptions from the schematics of AMC template (see 6.1) which provides more detailed information on how the mandatory MicroTCA® components should be used.

Figure 12: AMC connector pins

Figure 13: MicroTCA® mandatory components

| Pin Name  | Location | Direction | Description                                                                                                                                                                                                                                      |

|-----------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMC_PS1_N | A12      | IN        | Module presence detect, as defined in chapter "3.2.2 PS0# and PS1#" in the PICMG AMC.0 specification. The DMMC-STAMP SoM contains a Schottky diode between PS1# and PS#0.                                                                        |

| AMC_PS0_N | B11      | OUT       | Module presence detect, as defined in chapter "3.2.2 PS0# and PS1#" in the PICMG AMC.0 specification.                                                                                                                                            |

| AMC_EN_N  | D12      | IN        | MMC enable, as defined in chapter "3.2.3 ENABLE#" in the PICMG AMC.0 specification. This pin serves as a microcontroller reset and has to be pulled low to activate the microcontroller (this is normally done by MCH after presence detection). |

| AMC_GA2   | C12      | IN        | Geographic address (bit 2), as defined in chapter "3.2.1 Geographic Address [20] (GA[20])" in the PICMG AMC.0 specification. On DMMC-STAMP, there is a 3.3kOhm pull-up resistor on this pin.                                                     |

| AMC_GA1   | C11      | IN        | Geographic address (bit 1), as defined in chapter "3.2.1 Geographic Address [20] (GA[20])" in the PICMG AMC.0 specification. On DMMC-STAMP, there is a 3.3kOhm pull-up resistor on this pin.                                                     |

| AMC_GA0   | B12      | IN        | Geographic address (bit 0), as defined in chapter "3.2.1 Geographic Address [20] (GA[20])" in the PICMG AMC.0 specification. On DMMC-STAMP, there is a 3.3kOhm pull-up resistor on this pin.                                                     |

| AMC_SDA   | E12      | IN/OUT    | Serial data signal for IPMB, as defined in chapter "3.2.4 IPMB-L" in the PICMG AMC.0 specification. On DMMC-STAMP, there is a 3.3kOhm pull-up resistor on this pin.                                                                              |

| AMC_SCL   | E11      | IN        | Serial clock signal for IPMB, as defined in chapter "3.2.4 IPMB-L" in the PICMG AMC.0 specification. On DMMC-STAMP, there is a 3.3kOhm pull-up resistor on this pin.                                                                             |

Table 2: MCH/Backplane interface pin description

| Pin Name       | Location | Direction | Description                                                                                                                                                                            |

|----------------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTCA_HANDLE    | D11      | IN        | Hot-plug handle, shall be low when handle is inserted.<br>10kOhm pull-up (to 3.3V MP) is integrated on the DMMC-<br>STAMP SoM.                                                         |

| MTCA_LED_BLUE  | B7       | OUT       | Blue LED on the front-panel, use appropriate current-limiting resistors (output is at 3.3V; 24mA max.). According to the AMC.0 specification it shall be located on the bottom side    |

| MTCA_LED_GREEN | B6       | OUT       | LED 2 (green) on the front-panel, use appropriate current-limiting resistors (output is at 3.3V; 24mA max.). According to the AMC.0 specification it shall be located on the top side. |

| MTCA_LED_RED   | B5       | OUT       | LED 1 (red) on the front-panel, use appropriate current-limiting resistors (output is at 3.3V; 24mA max.). According to the AMC.0 specification it shall be located on the top side.   |

Table 3: Handle and LED pin description

Shown in Table 4 are the on-board sensor interface signals. The DMMC-STAMP SoM provides a local I2C bus for the management related sensors. Typically, another two MAX6626 temperature sensor are connected on the target AMC to measure the inlet (address 0x49) and outlet (address 0x4A) temperature and to report the value to the MCH. MAX6626 I2C temperature sensor (address 0x48), the parameter EEPROM (address 0x51) and the RTM I2C current selection potentiometer (address 0x2E) are already connected to the bus on the DMMC-STAMP SoM. These addresses must not be used by external devices. When using the DMMC-SDK, more sensors such as FPGA/SoC temperature sensors can be connected here.

| Pin Name | Location | Direction | <b>Description</b> |

|----------|----------|-----------|--------------------|

|          |          |           |                    |

| SNS_SCL | A10 | OUT | Sensor bus management serial clock. On DMMC-STAMP, there is a 10kOhm pull-up resistor on this pin. |

|---------|-----|-----|----------------------------------------------------------------------------------------------------|

| SNS_SDA | A9  | I/O | Sensor bus management serial data. On DMMC-STAMP, there is a 10kOhm pull-up resistor on this pin.  |

Table 4: Sensor interface pin description

Shown in Table 5 are the JTAG interface signals connected to the backplane. The voltage level for these pins is 3.3V derived from VCC+3V3.

| Pin Name | Location | Direction | Description                                                 |

|----------|----------|-----------|-------------------------------------------------------------|

| AMC_TMS  | M8       | IN        | JTAG mode select in - connect directly to AMC TMS (pin 166) |

| AMC_TCK  | M7       | IN        | JTAG clock input - connect directly to AMC TCK (pin 165)    |

| AMC_TDI  | M6       | IN        | JTAG data input - connect directly to AMC TDI (pin 169)     |

| AMC_TDO  | M5       | OUT       | JTAG data output - connect directly to AMC TDO (pin 168)    |

Table 5: AMC JTAG pin description (CPLD pins indicated in green)

### **5.2 Power Pins**

The DMMC-STAMP SoM accepts management power (VCC+3V3\_MP) and payload power (VCC+12V\_PP) as input. From the payload power the Power System (see 3.5) generates a dedicated 3.3V output (VCC+3V3\_MMC) that can be used on the target AMC. The 12V input to the RTM Hot-Plug Controller (see 3.4) is sourced from a dedicated power input pin (VCC\_12VPP\_IN). RTM management-and payload power are driven by separate pins (VCC\_RTM+3V3\_MP, VCC\_RTM+12V). In addition, for operating the FPGA/SoC interfaces at the CPLD (see 3.2) one bank voltage per FPGA/SoC interface (VCC\_FPGA1, VCC FPGA2) has to be supplied to the DMMC-STAMP SoM.

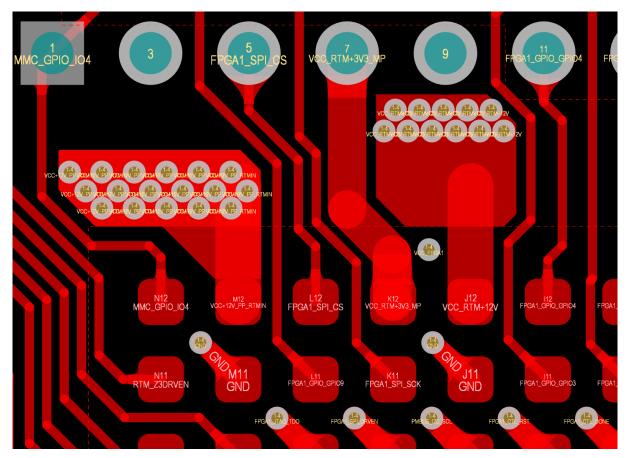

Shown in Figure 14 are exceptions from the schematics of AMC template (see 6.1.1). The 3V3 management- and 12V payload power is connected from the backplane (AMC connector) to LGA1A (pins A2 and F9 of the DMMC-STAMP SoM).

Figure 14: DMMC-STAMP SoM power input/output pins

| Pin Name      | Location                               | Direction | Description                                                                                                                                                                               |

|---------------|----------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC+3V3_MMC   | A4                                     | POWER OUT | Generated on the DMMC-STAMP SoM via DC/DC converter from payload power. external current draw: 250mA max                                                                                  |

| VCC+3V3_MP    | F9                                     | POWER IN  | Management power - connect to AMC connector                                                                                                                                               |

| VCC+12V_PP    | A2                                     | POWER IN  | Payload power - connect to AMC connector                                                                                                                                                  |

| VCC_FPGA1     | L6                                     | POWER IN  | See 5.4 FPGA/SoC Pins                                                                                                                                                                     |

| VCC_FPGA2     | L1                                     | POWER IN  |                                                                                                                                                                                           |

| VCC_12VPP_IN  | M12                                    | POWER IN  | See 5.5 RTM Pins                                                                                                                                                                          |

| VCC_3V3MP_RTM | K12                                    | POWER OUT |                                                                                                                                                                                           |

| VCC_12V_RTM   | J12                                    | POWER OUT |                                                                                                                                                                                           |

| GND           | A11, B4,<br>H4, J11,<br>M11, N3,<br>N6 | POWER GND | Ground                                                                                                                                                                                    |

| PGND          | B2, C2, D2POWER GND                    |           | Power ground of the DC/DC converter, to be connected to GND on the target AMC under the DMMC-STAMP SoM, directly (PGND and GND shall be connected to the same GND plane under the module) |

Table 6: Power Pin Description

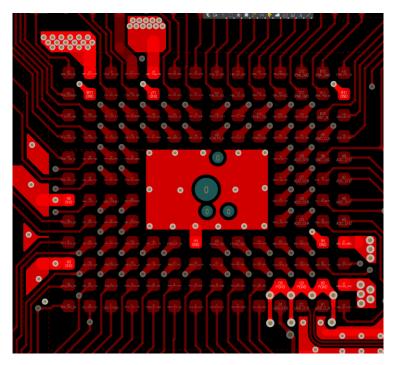

### 5.2.1 Global Power and Ground Routing Considerations

All power and ground nets should be routed with the lowest possible impedance. Multiple parallel type VII vias (resin-filled and copper-capped) placed directly inside the DMMC-STAMP pads are preferred. Power nets should be implemented as power polygons, and ground vias should connect directly to the solid internal ground planes of the PCB.

Figure 15: DMMC-STAMP Power and Ground connection using Type VII vias

When Type VII vias are not available (this is usually the case on cost-sensitive boards), large-diameter vias should be used -preferably several in parallel- together with wide traces to connect to the DMMC-STAMP power and ground pads. Inside the board, use solid power polygons to keep impedance low. Power polygon layer transitions should always be done with multiple vias in parallel. Ground pads should connect directly into a large ground plane located immediately beneath the DMMC-STAMP.

Figure 16: DMMC-STAMP Power and Ground connection using standard vias

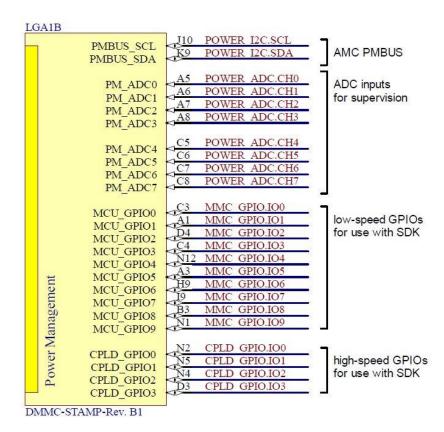

### **5.3 Target AMC Power Management Pins**

The DMMC-STAMP SoM provides the required infrastructure for a target AMC power management. With the pre-programmed firmware, the target AMC power management is limited to the report of the ADC voltages. The control of devices on the I2C bus is not foreseen and has to be implemented within a customized firmware using the DMMC-SDK (see 6.2).

Listed below are some additional information for the target AMC power supervision:

- The MCU can read voltages via 8 ADC inputs.

- All ADC inputs have a resolution of 12 bits and allow input voltages from 0 to 1 V.

- The MCU can interface PMBUS™ DC/DC converters or PMBUS™ power managers via a dedicated I2C bus (SDK required). On this bus address 0x70 is reserved for an I2C multiplexer located on the DMMC-STAMP.

- The MCU provides 10 GPIO pins with a 3.3 V level, derived from management power (SDK required to implement user functions, such as power enables).

- The MCU provides 4 CPLD GPIO pins with 3.3 V level, derived from payload power (SDK required to implement user functions, such as power enables).

Shown in Figure 17 are exceptions from the schematics of AMC template (see 6.1) showing the interface described above.

Figure 17:DMMC-STAMP power management pins

| Pin Name  | Location | Direction | Description                                                                                                         |

|-----------|----------|-----------|---------------------------------------------------------------------------------------------------------------------|

| PMBUS_SDA | K9       | I/O       | PMBUS™ management serial clock. On DMMC-STAMP, there is a 5kOhm-equivalent pull-up resistor on this pin.            |

| PMBUS_SCL | J10      | OUT       | PMBUS <sup>™</sup> management serial data. On DMMC-STAMP, there is a 5kOhm-equivalent pull-up resistor on this pin. |

Table 7: Target AMC PMBUS™ Pin Description

| Pin Name | Location | Direction | Description           |

|----------|----------|-----------|-----------------------|

| PM_ADC0  | A5       | IN        | ADC inputs, channel 0 |

| PM_ADC1  | A6       | IN        | ADC inputs, channel 1 |

| PM_ADC2  | A7       | IN        | ADC inputs, channel 2 |

| PM_ADC3  | A8       | IN        | ADC inputs, channel 3 |

| PM_ADC4  | C5       | IN        | ADC inputs, channel 4 |

| PM_ADC5  | C6       | IN        | ADC inputs, channel 5 |

| PM_ADC6  | C7       | IN        | ADC inputs, channel 6 |

| PM_ADC7  | C8       | IN        | ADC inputs, channel 7 |

Table 8: ADC pin description for target AMC power monitoring

Table 9 shows the low-speed GPIOs controlled by the MCU which are operating in the management power domain (always available when management power is present).

| Pin Name  | Location | Direction | Description                                |

|-----------|----------|-----------|--------------------------------------------|

| MCU_GPIO0 | C3       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO1 | A1       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO2 | D4       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO3 | C4       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO4 | N12      | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO5 | A3       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO6 | H9       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO7 | 19       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO8 | В3       | IN        | Custom user function in MCU (SDK required) |

| MCU_GPIO9 | N1       | IN        | Custom user function in MCU (SDK required) |

Table 9: Low-speed MCU GPIO pin description

Table 10 shows the high-speed GPIOs controlled by the CPLD which are operating in the payload power domain with fixed 3.3V levels.

| Pin Name   | Location | Direction | Description                                 |

|------------|----------|-----------|---------------------------------------------|

| CPLD_GPIO0 | N2       | I/O       | Custom user function in CPLD (SDK required) |

| CPLD_GPIO1 | N5       | I/O       | Custom user function in CPLD (SDK required) |

| CPLD_GPIO2 | N4       | I/O       | Custom user function in CPLD (SDK required) |

| CPLD_GPIO3 | D3       | I/O       | Custom user function in CPLD (SDK required) |

Table 10: High-speed CPLD GPIO pin description

#### 5.4 FPGA/SoC Pins

The DMMC-STAMP SoM is able to interface up to two FPGAs/SoC via two separated LGA interface "banks". Both "banks" are identical in terms of pin functionality where the pins itself operate at the voltage level defined by the input of the VCC\_FPGA[1/2] pin.

Given below are some more detailed information about the FPGA interface pin functionality:

- UART (RXD/TXD): provides a virtual COM port interface to the FPGAs/SoCs that is accessible

via the DMMC-STAMP USB-to-UART interface (see 3.3). There is only one FPGA/SoC UART

interface which can be directed to the USB at one time (multiplexed within the CPLD). When

the DMMC-SDK is used, one or both of these ports can be exposed over the network by using

mmcterm (see 6.4).

- Configuration control signals: PROG, INIT, DONE, RESET

- JTAG interface that can be connected to the DMMC-STAMP SoM JTAG connector (multiplexed within the CPLD).

- SPI FLASH configuration interface which allows an in-system programming of the FPGAs/SoCs

FLASH via HPM. This is very useful to allow the user to re-program the on-board FPGAs/SoCs

without any additional software or hardware. A redundant SPI memory is supported as well

(used to store "golden" image).

- GPIO interface: General-Purpose IO pins that can be used for a custom firmware. Users of the DMMC-STAMP SoM can use the DMMC-SDK to add their own functionality to these pins.

- Input voltage: VCC\_FPGA[1/2] is an input pin and defines the output level of all signals of the FPGA/SoC interface "bank", i.e. if the FPGA[1/2] configuration interface (typically in Bank 0) is operated at a 1.8V level, this voltage has to be fed to the VCC\_FPGA[1/2] pin.

### 5.4.1 MMC Stamp Mailbox

The Mailbox is an optional I<sup>2</sup>C-based communication interface between the DMMC-STAMP and the FPGA, primarily intended for SoCs running an embedded OS. It is available only to customers who have purchased the DMMC-STAMP SDK. The Mailbox is enabled by compiling user-specific CPLD code that implements the required functionality. This user-specific CPLD image is usually integrated into the MMC firmware while compiling the SDK code. This ensures that CPLD updates are automatically deployed with the MMC firmware. CPLD firmware updates are fully managed by the MMC firmware and run automatically without any user-intervention when a CPLD contains an outdated image.

Using the Mailbox, the FPGA can communicate directly with the DMMC-STAMP, enabling controlled or graceful OS shutdown sequences.

#### **Purpose and functionality**

System information exchange:

The MMC-STAMP emulates a standard AT24Cxx I²C EEPROM interface inside its CPLD. The hard-coded address is 0x2A by default. This allows the FPGA to access relevant data such as MAC address, MTCA slot number, temperature values, and other operational parameters. During operating system boot, existing drivers that support reading from I²C EEPROMs can use the Mailbox without modification, treating it like a standard EEPROM device. After boot, a Yocto-based daemon takes over and manages continuous communication with the MMC-STAMP.

Controlled shutdown handling:

The Mailbox enables the MMC to signal the FPGA and the operating system when a shutdown or reboot is required, for example when the handle is pulled or the MCH initiates a reset. This mechanism ensures the operating system can shut down properly. Without it, unexpected power loss may occur, leading to boot image corruption and unstable system behavior.

System integration:

By providing a structured communication channel, the Mailbox allows close coordination between hardware management functions on the MMC and application logic implemented on the FPGA. In the absence of the Mailbox, the FPGA operates without access to management data and without the ability to handle controlled power transitions.

#### Implementation

The MMC Mailbox is implemented inside the STAMP CPLD. On the hardware side, the user must connect two FPGAx\_GPIOy pins on the STAMP to serve as the  $I^2C$  interface. These pins can be chosen arbitrarily, provided that the correct voltage level is ensured. External pull-up resistors, typically  $10~k\Omega$ , must be added to complete the  $I^2C$  bus connection.

On the FPGA side, two pins of the Processing System (PS) should be chosen, so that the Mailbox functionality is available before the Programmable Logic (PL) has been initialized. Ideally, I²C-capable PS pins are selected. However, this is not mandatory: a software-based I²C implementation (soft-I²C) will also work on any PS I/O pin, which is fully supported by Yocto. Care must be taken to ensure that the FPGAx\_GPIOy pins on the STAMP and the chosen PS bank operate at the same voltage level.

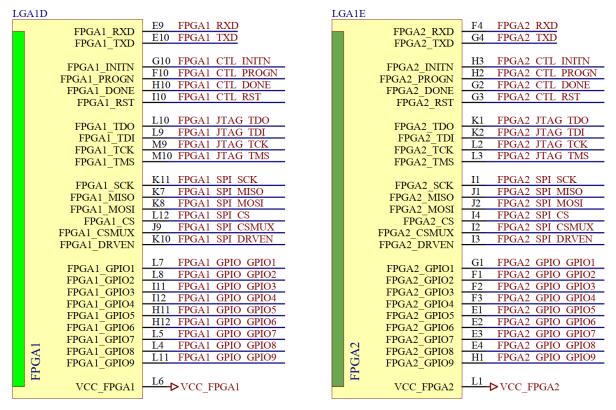

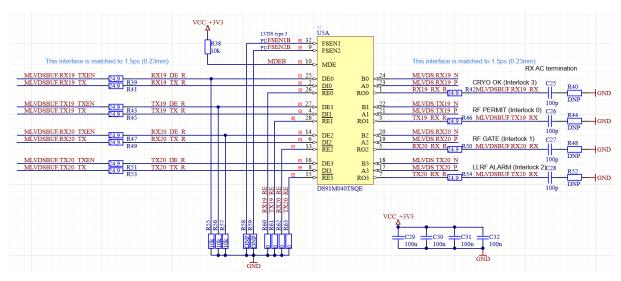

Shown in Figure 18 are exceptions from the schematics of AMC template (see 6.1) showing the FPGA/SoC interface described above.

Figure 18: DMMC-STAMP FPGA/SoC interface pins

| Pin Name | Location | Direction | <b>Description</b> |

|----------|----------|-----------|--------------------|

|----------|----------|-----------|--------------------|

| FPGA[1/2]_RXD | E9/F4  | OUT | FPGA[1/2] UART receive  |

|---------------|--------|-----|-------------------------|

| FPGA[1/2]_TXD | E10/G4 | IN  | FPGA[1/2] UART transmit |

Table 11: FPGA/SoC UART pin description

Table 12 shows the FPGA/SoC JTAG signals which can be forwarded either from a JTAG connector on the target AMC or from the AMC backplane connector. These signals are multiplexed within the DMMC-STAMP SoM CPLD.

Pin Name Location Direction Description

| FPGA[1/2]_JTAG.TMS | M10/L3 | OUT | JTAG Mode Select - connect to TMS pin of FPGA[1/2]  |

|--------------------|--------|-----|-----------------------------------------------------|

| FPGA[1/2]_JTAG.TCK | M9/L2  | OUT | JTAG Clock Output - connect to TCK pin of FPGA[1/2] |

| FPGA[1/2]_JTAG.TDI | L9/K2  | OUT | JTAG Data Input - connect to TDI pin of FPGA[1/2]   |

| FPGA[1/2]_JTAG.TDO | L10/K1 | IN  | JTAG DATA Output - connect to TDO pin of FPGA[1/2]  |

Table 12: FPGA/SoC JTAG pin description

| Pin Name        | Location | Direction | Description                                                                                                                                                                                                       |

|-----------------|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA[1/2]_RST   | I10/G3   | OUT       | User firmware reset (active high), connect to any GPIO pin of the FPGA/SoC, a user firmware reset can be initiated with this pin                                                                                  |

| FPGA[1/2]_DONE  | H10/G2   | IN        | A high signal on the DONE pin indicates completion of the configuration sequence. Connect to DONE on FPGA[1/2]. (a pull-up is needed according to the specific FPGA/SoC, see FPGA/SoC vendor configuration guide) |

| FPGA[1/2]_INITN | G10/H3   | IN        | Active-Low FPGA/SoC initialization pin or configuration error signal. Connect to INIT_B on FPGA[1/2] (a pull-up is needed according to the specific FPGA/SoC, see FPGA/SoC vendor configuration guide)            |

| FPGA[1/2]_PROGN | F10/H2   | OUT       | Active-Low reset to configuration logic. Connect to PROGRAM_B on FPGA[1/2]                                                                                                                                        |

Table 13: FPGA/SoC Control pin description

Table 14 shows the fast DMMC-STAMP CPLD GPIO pins for FPGA/SoC control signals. DESY typically connects Bank 0 mode pins and additional FPGA/SoC control pins here (such as PS\_POR\_B, PS\_SRST, PS\_ERROR\_OUT, PS\_ERROR\_STATUS, POR\_OVERRIDE) and the MMC Mailbox. To implement a custom CPLD configuration image, the DMMC-SDK is required.

| Pin Name             | Location | Direction | Description                                 |

|----------------------|----------|-----------|---------------------------------------------|

| FPGA[1/2]_GPIO.GPIO9 | L11/H1   | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO8 | L4/E4    | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO7 | L5/E3    | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO6 | H12/E2   | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO5 | H11/E1   | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO4 | I12/F3   | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO3 | l11/F2   | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO2 | L8/F1    | I/O       | Custom user function in CPLD (SDK required) |

| FPGA[1/2]_GPIO.GPIO1 | L7/G1    | I/O       | Custom user function in CPLD (SDK required) |

|                      |          |           |                                             |

Table 14: FPGA/SoC GPIO pin description

Table 15 shows the FPGA/SoC SPI Flash configuration control pins. For operating a SPI Flash configuration memory on the target AMC two external components are needed (see below).

| Pin Name            | Location | Direction | Description                                                                                                                       |

|---------------------|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| FPGA[1/2]_SPI.CS    | L12/I4   | OUT       | MOSI for FLASH access (connect to buffer)                                                                                         |

| FPGA[1/2]_SPI.DRVEN | K10/I3   | OUT       | Driver activate signal (active_low). When the DMMC-STAMP wishes to access the SPI FLASH memories, the DRVEN signal is driven low. |

| FPGA[1/2]_SPI.CSMUX | J9/I2    | OUT       | Chip select multiplexer control (selects primary=high or redundant=low memory)                                                    |

| FPGA[1/2]_SPI.SCK   | K11/I1   | OUT       | SCK for FLASH access (connect to buffer)                                                                                          |

| FPGA[1/2]_SPI.MOSI  | K8/J2    | OUT       | MOSI for FLASH access (connect to buffer)                                                                                         |

| FPGA[1/2]_SPI.MISO  | K7/J1    | IN        | MISO for FLASH access (connect to buffer)                                                                                         |

Table 15: FPGA/SoC SPI Flash control pin description

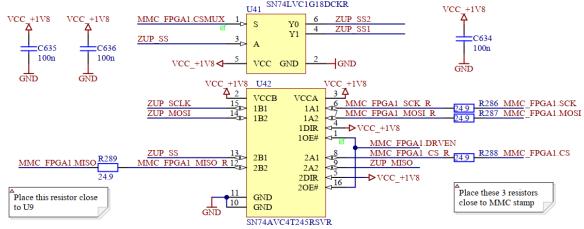

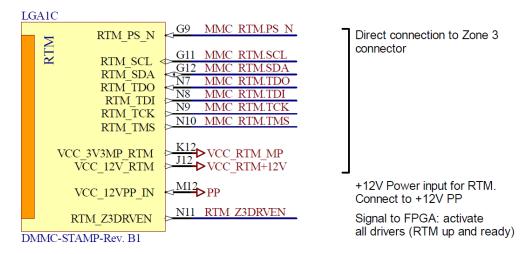

#### 5.4.2 Flash Access Scheme

In previous DESY MMC designs, the FLASH interface was routed to the MMC CPLD, directly. This simple scheme is not possible anymore. It is assumed, that the DMMC-STAMP SoM is placed far away from the FLASH memories which means that routing fast (100 MHz+) FLASH traces over long lines is not possible. To address this issue, the DMMC-STAMP SoM is separated via a discrete buffer and a discrete demultiplexer chip. This means that the traces can be kept short between the FLASH and the additional ICs in between so that signal integrity is not severely influenced (see Figure 19 to Figure 21).

Selection of primary/redundant FLASH memory:

- A 1-of-2 demultiplexer chip (e.g. 74LVC1G18) is used for decoding the FPGA/SoC chip select signal and for routing this signal to one of the two SPI memories. The chip should be placed next to the SPI memories, so that the CS path has minimal additional length.

- The DMMC-STAMP SoM controls the "select" input of the demultiplexer via the CSMUX output so that the primary/secondary memory can be selected via MMC CLI.

- If the 74LVC1G18 is used, pull-up resistors are needed on the CS lines at the FLASH memory.

#### Access to the SPI FLASH memories

- In order to access the FLASH memories, the DMMC-STAMP SoM pulls the FPGA/SoC into reset (PROG\_N). The FPGA tri-states all configuration lines including the FLASH interface.

- When the FPGA/SoC is de-activated, the FLASH memories are reset, to terminate any special modes (e.g. x4 mode) that have been used for configuration and allow access in standard SPI mode.

- With the FPGA in reset, the external buffer is activated by pulling the DRVEN signal low. In this

mode, the DMMC-STAMP SoM can access the SPI memories exclusively.

- All SPI pins that are unused in standard operation mode (HOLD/DQ3, WP/DQ2 etc.) need proper pull-ups or pull-downs so that these pins do not float during DMMC-STAMP SoM FLASH access.

Figure 19: SPI Flash configuration memory connection scheme

# FLASH interface direction switch (Firmware update via MMC)

Figure 20: SPI Flash multiplexer implementation

Figure 21: SPI Flash implementation

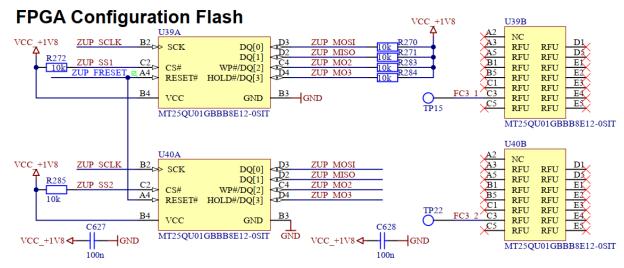

### 5.5 RTM Pins

The DMMC-STAMP SoM can manage one MicroTCA.4 compliant Rear Transition Module (RTM). It provides power control, including inrush-current limiting and a programmable overcurrent detection. Shown in Figure 22 is an exception from the schematics of AMC template (see 6.1) showing the RTM interface described here.

Figure 22: RTM interface pins

| Pin Name      | Location | Direction | Description                                                                                                            |

|---------------|----------|-----------|------------------------------------------------------------------------------------------------------------------------|

| VCC+12VPP_IN  | M12      | POWER IN  | Payload power input for RTM - connect to 12V payload power with a low-impedance power polygon to prevent voltage drop. |

| VCC_3V3MP_RTM | K12      | OUT       | Management power for RTM - connect to the Zone 3 connector                                                             |

| VCC_12V_RTM   | J12      | OUT       | Payload power for RTM - connect to the Zone 3 connector                                                                |

Table 16: RTM power pin description

Table 17 shows the RTM management signals. These signals are translated to the 3V3MP\_RTM power domain. Pull-ups are integrated on the DMMC-STAMP SoM. All I2C signals are tri-stated when the RTM is not inserted.

| Pin Name | Location | Direction | Description                                                                                                                                                        |  |

|----------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RTM_SCL  | G11      | OUT       | RTM management serial clock. On DMMC-STAMP, there is an 5kOhm-equivalent pull-up resistor on this pin. Do not connect an additional pull-up resistors to this pin. |  |

| RTM_SDA  | G12      | I/O       | RTM management serial data. On DMMC-STAMP, there is an 5kOhm-equivalent pull-up resistor on this pin. Do not connect an additional pull-up resistors to this pin.  |  |

| RTM_PS_N | G9       | IN        | RTM presence detect. Route to the PS# pin on the Zone 3 connector. On DMMC-STAMP, there is a 10kOhm pull-up re on this pin.                                        |  |

Table 17: RTM management signal pin description

Table 18 shows the FPGA/SoC tri-state control signal which will be used as a drive-enable flag for the Zone3 data interface signals (to/from the FPGA/SoC). The firmware on the target AMC FPGA/SoC has to disable all drivers to the RTM if this signal is low. Using this signal, RTM hot-plug support is achieved since the Zone 3 pins can be set to tri-state during RTM insertion or removal.

#### Attention:

The voltage level on this pin is 3.3V. Voltage translation (e.g. with a resistive divider) to the FPGA/SoC bank voltage is usually required. Alternatively, this information can be output on any FPGA[1/2]\_GPIO pin since these signals are already translated to FPGA/SoC bank voltage (DMMC-SDK required).

| Pin Name    | Location | Direction | Description                                                                   |

|-------------|----------|-----------|-------------------------------------------------------------------------------|

| RTM_Z3DRVEN | N11      | OUT       | This pin goes high when the RTM is in M4 state and is low in all other states |

Table 18: FPGA/SoC tri-state control pin description

Table 19 shows the RTM JTAG access signal which operate in the +3.3V payload power domain. All JTAG signals are tri-stated when the RTM is not inserted.

| Pin Name | Location | Direction | Description                                                                              |

|----------|----------|-----------|------------------------------------------------------------------------------------------|

| RTM_TMS  | N10      | OUT       | JTAG Mode Select - connect to TMS pin on RTM connector                                   |

| RTM_TCK  | N9       | OUT       | JTAG Clock Output - connect to TCK pin on RTM connector                                  |

| RTM_TDI  | N8       | OUT       | TDI - connect to TDI pin of Z3 RTM connector (directly routed to TDI pin of FPGA on RTM) |

| RTM_TDO  | N7       | IN        | TDO - connect to TDO pin of Z3 RTM connector (directly routed to TDO pin of FPGA on RTM) |

Table 19: RTM JTAG pin description

### 5.5.1 RTM start-up power limit control

To implement RTM current limiting, DMMC-STAMP uses a power distribution switch designed to control inrush and actively limit load current. It monitors the voltage across an external sense resistor and adjusts the gate of an external MOSFET to regulate and cap current. When the load current rises and the sensed voltage reaches the internal threshold, the controller begins throttling the MOSFET, which behaves like a variable resistor during this phase, continuously modulating it to maintain the current at the programmed limit. This mechanism regulates inrush, preventing excessive surges when charging RTM input capacitors, and it also activates during RTM failures when current demands exceed the MicroTCA specification. During this limiting phase, which lasts approximately 300 ms, the MOSFET operates in its linear region. During that phase, the MOSFET is operated near its Safe Operating Area limit. If the excessive current persists beyond this period, the RTM is shut down and a fault is indicated.

During startup, DMMC-STAMP temporarily raises the current limit moderately above 30 W to accommodate higher inrush demands. Once startup is complete, the limit returns to just above 30 W for normal operation. This approach allows safe powering of a constant 30 W load while handling inrush, ensuring stable startup and compliance with MicroTCA specifications.

Users can configure the current limit through the SDK. When exceeding the specified MicroTCA envelope (i.e., setting the limit above 30W), it is critical that any custom settings respect the MOSFET's

SOA; exceeding it may damage the device, for example by forcing it into a constant-on state, potentially compromising the system.

### 5.5.2 RTM-specific Power Routing Considerations

According to the MTCA standard, an RTM can draw up to 30 W, corresponding to 2.5 A at 12 V. The DMMC-STAMP temporarily increases this limit to about 50 W during RTM activation to allow faster charging of the RTM input capacitors, which corresponds to roughly 4 A. Many RTMs are sensitive to drops on their supply voltage. Because the MicroTCA power supply operates in a 10-14 V range, and additional losses occur on the AMC backplane and AMC connector, it is important to avoid introducing further voltage drop around the DMMC-STAMP. The resistance of the 12 V path feeding the DMMC-STAMP should therefore be kept as low as possible. Track width and layer transitions require particular attention. We recommend placing five vias directly into the 12 V power pads of the RTM power supply using Type VII vias. Power for the RTM should be routed exclusively through robust power polygons, and any layer transitions should use multiple parallel vias to minimize resistance.

The net VCC+12VPP\_IN (RTM input power) should be implemented as a large passive internal power polygon. The length and thickness of the power polygon on the VCC\_12V\_RTM net (power output towards RTM) should be chosen to keep the path voltage drop low, ideally around 0.1 V or better.

Management power consumption of the AMC and RTM are generally low. Because of that, the management rail receives no priority within the AMC backplane. To prevent additional voltage drop, a 1 mm wide trace should be routed from the MMC-STAMP to the Zone 3 connector.

Figure 23: RTM power routing example using Type VII vias

Figure 24: RTM power routing example using standard vias

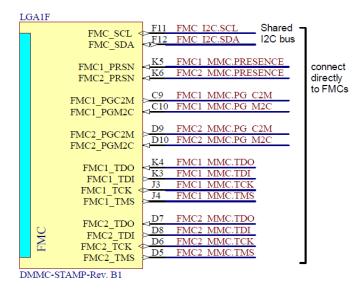

### 5.6 FMC Pins

When the DMMC-SDK is used, the DMMC-STAMP SoM can manage up to two FPGA Mezzanine Card (FMC) modules. All pins have 3.3V level according to the FMC specification. The I2C bus is shared between both modules. Make sure that the GA pins of the FMC connectors differ from each other - only in this case the addresses of the FMC modules are unique and no address conflicts occur (see FMC specification). The address 0x70 is reserved on this bus as this is the address of the I2C multiplexer located on the DMMC-STAMP SoM.

All pins (except I2C) are routed to the DMMC-STAMP CPLD. Although the CPLD FMC Pins can be reassigned using the SDK, these pins are not indeneded for custom functions (i.e. not related to FMC) since the FMC detection and activation logic may interfere with the desired user functions.

Please note that level translation is necessary in case levels different than 3.3V are desired.

Shown in is an exception from the schematics of AMC template (see 6.1) showing the FMC interface described here.

Figure 25: FMC interface pins

| Pin Name       | Location | Direction | Description                                                                                                                                                                                                                                                           |

|----------------|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FMC_SCL        | F11      | OUT       | FMC management serial clock (shared between FMC1 and FMC2). Ensure different I2C addresses of the FMC modules by assigning the GA[01] pins of the FMC connector different for both modules. On DMMC-STAMP, there is an 5kOhm-equivalent pull-up resistor on this pin. |

| FMC_SDA        | F12      | I/O       | FMC management serial data (shared between FMC1 and FMC2). On DMMC-STAMP, there is a 10kOhm pull-up resistor on this pin. On DMMC-STAMP, there is an 5kOhm-equivalent pull-up resistor on this pin.                                                                   |

| FMC[1/2]_PRSN  | K5/K6    | IN        | FMC presence detection. Connect to presence pin of FMC connector. MCU-internal weak pull-up is included in the DMMC-STAMP (see ATSAM4L spec. —> References)                                                                                                           |

| FMC[1/2]_PGC2M | C9/D9    | OUT       | Power-good signal that is asserted by DMMC-STAMP                                                                                                                                                                                                                      |

| FMC[1/2]_PGM2C | C10/D10  | IN        | Power-good signal that is asserted by FMC module CPLD-internal weak pull-up is included in the DMMC-STAMP (see MachXO2 spec. —> References)                                                                                                                           |

Table 20: FMC management pin description

| Pin Name     | Location | Direction | Description                                        |  |

|--------------|----------|-----------|----------------------------------------------------|--|

| FMC[1/2]_TMS | J4/D5    | OUT       | JTAG Mode Select - connect to TMS pin on FMC[1/2]  |  |

| FMC[1/2]_TCK | J3/D6    | OUT       | JTAG Clock Output - connect to TCK pin on FMC[1/2] |  |

| FMC[1/2]_TDI | K3/D8    | OUT       | JTAG Data Input - connect to TDI pin on FMC[1/2]   |  |

| FMC[1/2]_TDO | K4/D7    | IN        | JTAG Data Output - connect to TDO pin on FMC[1/2]  |  |

Table 21: FMC JTAG pin description

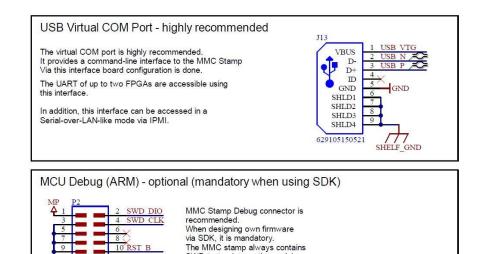

# 5.7 Debug Pins

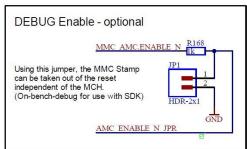

The DMMC-STAMP SoM is equipped with a pre-programmed firmware image for the on-board CPLD and MCU providing access to the debug interfaces described here. It is up to the user to decide which debug interface to route on the target AMC (see Figure 26):

- USB: Provides CLI access to MMC and user FPGAs. Highly recommended, no diagnostic output or user configuration is possible without USB connector.

- JTAG: provides access to the FPGAs/SoC and the DMMC-STAMP SoM CPLD, fallback programming option for CPLD

- Cortex-M4 MCU debug access, recommended when using the DMMC-SDK to program userdefined functions into the DMMC-STAMP

SWD test points on the module.

TSH-105-01-L-DV-K

Figure 26: DMMC-STAMP debug interfaces

Shown in Table 22 are the central JTAG connector pins. The voltage level for these pins is 3.3V which is derived from VCC+3V3.

| Pin Name | Location | Direction | Description                                                         |

|----------|----------|-----------|---------------------------------------------------------------------|

| CON_TMS  | M4       | OUT       | JTAG Mode Select IN - Connect directly to TMS on onboard connector. |

| CON_TCK  | M3       | OUT       | JTAG Clock Input - Connect directly to TCK on on-board connector.   |

| CON_TDI  | M2       | OUT       | JTAG Data Input - Connect directly to TDI on on-board connector.    |

| CON_TDO  | M1       | IN        | JTAG DATA Output - Connect directly to TDO on onboard connector.    |

Table 22: Central JTAG connector pin description

# **Debug Connector**

Figure 27: DMMC-STAMP debug interfaces

| Pin Name | Location | Direction   | Description                                                                                                                                                                                                             |

|----------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_VTG  | D1       | POWER INPUT | +5V from USB connector. This voltage is used to power the CP2105 USB-to-UART bridge (host-powered). The DMMC-STAMP translates all UART signals to the MP (MCU) and PP (CPLD) domain. Connect directly to USB connector. |

| USB_DP   | C1       | IN/OUT      | USB Data+. Connect directly to USB connector.                                                                                                                                                                           |

| USB_DM   | B1       | IN/OUT      | USB Data Connect directly to USB connector.                                                                                                                                                                             |

Table 23: USB connector pin description

| Pin Name | Location | Direction | Description                                                                                                                                                                                                                                                                                                             |

|----------|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWD_DIO  | B8       | IN/OUT    | Serial Wire Debug DATA in/out (parallel to TC2030 connector). On DMMC-STAMP, there is an 10kOhm pull-up resistor on this pin.                                                                                                                                                                                           |

| SWD_CLK  | B9       | IN        | Serial Wire Debug CLOCK (parallel to TC2030 connector). On DMMC-STAMP, there is an 10kOhm pull-up resistor on this pin.                                                                                                                                                                                                 |

| RST_B    | B10      | IN        | Microcontroller Reset IO (parallel to TC2030 connector). This line is gated by the IPMI Reset. To release the microcontroller from Reset, the MCH has to drive AMC_EN_N low. For on-desk operation (without MCH) the AMC_EN_N has to be grounded (e.g. with a Jumper) to allow normal operation of the Microcontroller. |

Table 24: SWD pin description

# 5.8 Interlock forwarding to RTM